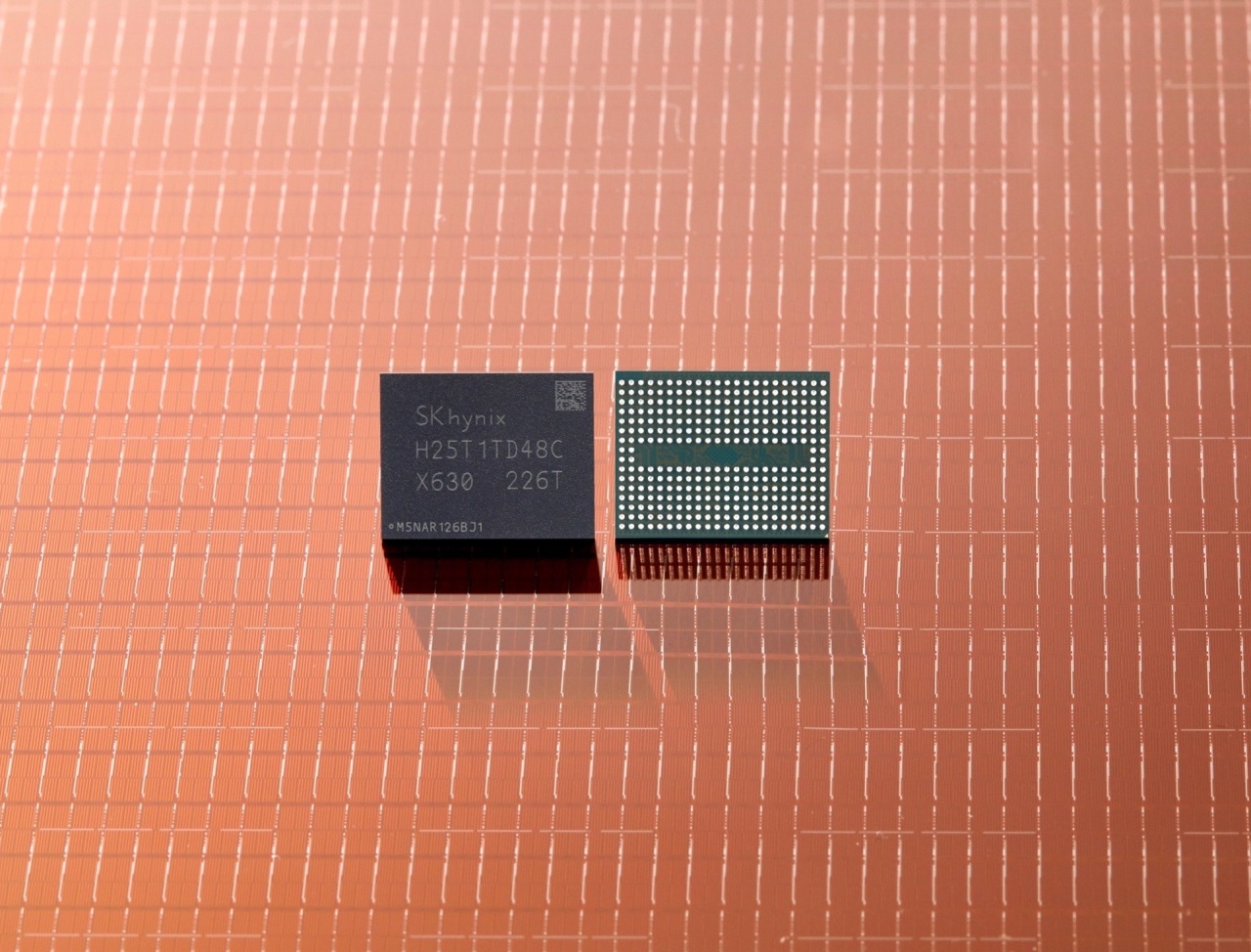

SK hynix said Tuesday that it had unveiled plans to mass-produce the industry‘s first 238-layer four-dimensional NAND flash memory in the first half of 2023.

At the Flash Memory Summit of 2022 held in Santa Clara, California, Choi Jung-dal, head of NAND development at SK hynix, said the newest NAND flash, which boasts the highest layer count and highest triple-level cell density in the industry, has been sampled by clients after the development was complete in July.

The technological breakthrough by the South Korean chipmaker has increased the speed of data transfer to 2.4 gigabits per second, up 50 percent compared to the predecessor, a 176-layer 4-D NAND flash that was developed in December 2020.

Moreover, the brand-new chip is more energy-efficient, cutting the power consumption by 21 percent compared with the predecessor. Its package size has also been reduced, increasing the manufacturing efficiency by 34 percent from the previous generation of chips.

The news comes a week after its US memory rival Micron Technology announced that it had shipped a 232-layer NAND flash product -- a product that was then considered to have the highest layer count.

SK hynix said the 238-layer 4-D NAND flash with the 512-gigabit storage capacity will first come with a client solid-state drive for personal computers, while the company plans to roll out more products compatible with smartphones and servers. Also, the NAND flash memory product with a 1-terabit capacity will debut in 2023.

SK hynix developed the world’s first 4-D NAND flash in 2018. Since then, the company has applied technologies such as charge trap flash -- a technology that reduces stress on memory through insulator layers -- and peri under cell -- placing peripheral circuits under the cell array to maximize production efficiency -- for the 4-D stacking technology.

(consnow@heraldcorp.com)

At the Flash Memory Summit of 2022 held in Santa Clara, California, Choi Jung-dal, head of NAND development at SK hynix, said the newest NAND flash, which boasts the highest layer count and highest triple-level cell density in the industry, has been sampled by clients after the development was complete in July.

The technological breakthrough by the South Korean chipmaker has increased the speed of data transfer to 2.4 gigabits per second, up 50 percent compared to the predecessor, a 176-layer 4-D NAND flash that was developed in December 2020.

Moreover, the brand-new chip is more energy-efficient, cutting the power consumption by 21 percent compared with the predecessor. Its package size has also been reduced, increasing the manufacturing efficiency by 34 percent from the previous generation of chips.

The news comes a week after its US memory rival Micron Technology announced that it had shipped a 232-layer NAND flash product -- a product that was then considered to have the highest layer count.

SK hynix said the 238-layer 4-D NAND flash with the 512-gigabit storage capacity will first come with a client solid-state drive for personal computers, while the company plans to roll out more products compatible with smartphones and servers. Also, the NAND flash memory product with a 1-terabit capacity will debut in 2023.

SK hynix developed the world’s first 4-D NAND flash in 2018. Since then, the company has applied technologies such as charge trap flash -- a technology that reduces stress on memory through insulator layers -- and peri under cell -- placing peripheral circuits under the cell array to maximize production efficiency -- for the 4-D stacking technology.

(consnow@heraldcorp.com)

![[Kim Seong-kon] Democracy and the future of South Korea](http://res.heraldm.com/phpwas/restmb_idxmake.php?idx=644&simg=/content/image/2024/04/16/20240416050802_0.jpg&u=)

![[Today’s K-pop] Zico drops snippet of collaboration with Jennie](http://res.heraldm.com/phpwas/restmb_idxmake.php?idx=642&simg=/content/image/2024/04/18/20240418050702_0.jpg&u=)